verilog编写中时钟和复位信号的逻辑

复位信号在数字电路中常见为低电平复位rst_n

为什么使用低电平复位多,因为上电过程中复位信号先为0,等超过阈值之后才是1,也就是说上电过程中一直复位住电路,直到超过阈值才是1,也就是说,上电过程中一直复位住电路,直到电源电压达到一定幅度后才释放。

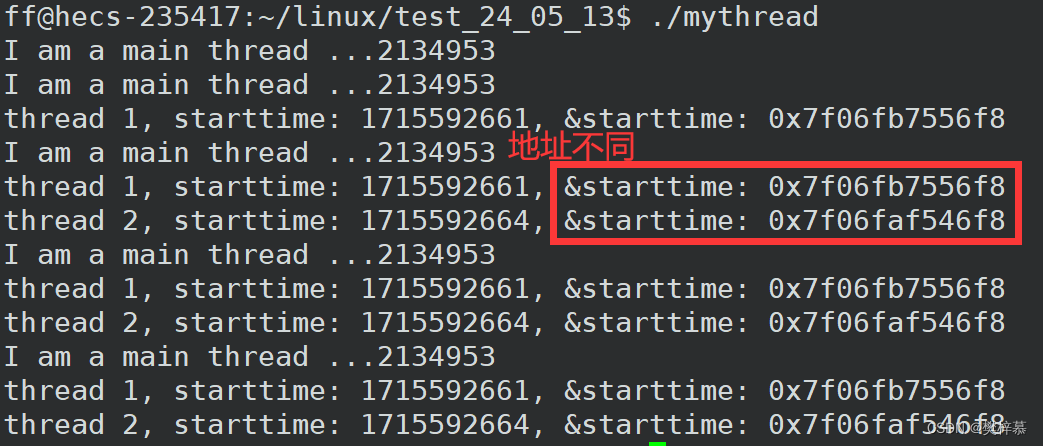

异步复位同步释放原则

异步复位同步释放原则是指一个寄存器的复位信号随时可以复位,不必考虑该寄存器的时钟信号在哪一个相位上。

同步释放指一个寄存器的复位信号从复位态回到释放状态的时机,必须要与该寄存器的时钟信号保持同步关系。

对复位信号什么时候复位没有要求,而对什么时候释放有严格要求。

在这里我想到了一个时序上的问题 在之前做SOC时 添加的zynq使用 block design 有些使用的异步时钟 最终还是需要分别接出到专门管理异步时序的电路模块上去